|

We use this page to highlight various technology areas where Anchor Hill has interesting or unusual solutions to common or uncommon problems.

The highlighted topic will change from time to time, but don't worry, we'll archive the cool ones so that you don't miss anything!

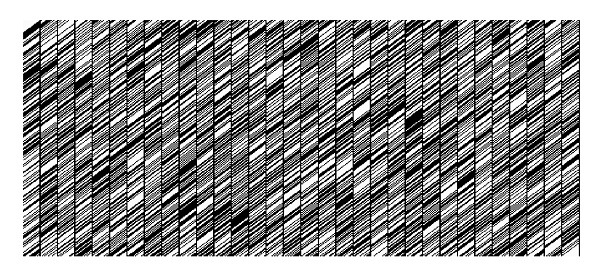

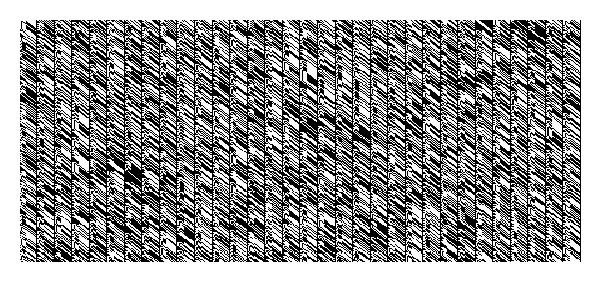

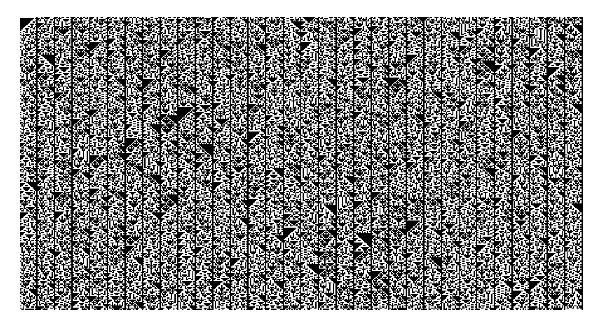

Using Visual Methods to Test Stochastic Processes Sometimes Yields Cool Pictures

This images shown are graphic representations of the entire Maximal Length sequence generated using different types of ML digitial shift registers. All are 13-bit registers. The first uses a Fibonacci LFSR implementation, the second is a Galois LFSR, and the third is a 13-bit CASR. Click on each image for a larger version, suitable for framing.

One way to test a Pseudo-Random Binary Sequence (PRBS) shift register is to create an image of the generated sequence. Shown here are three such images, generated with two types of Linear Feedback Shift Register (LFSR) and a Cellular Automata Shift Register (CASR) with the binary register state of each captured after each clock cycle. Black pixels indicate the locations of '0' bits and white pixels are '1' bits. Inspection of the image can reveal any undesirable patterns that may reduce the effective "randomness" of the sequence. Other properties, like Maximal Length (ML), can be quickly verified as well. It can be easily seen that the "randomness" of each technique has different qualities, with the Fibonacci LFSR having some distinct structure and not looking very random, despite having reasonable random statistics and being a true ML sequence. The Galois LFSR is visually a bit better, but the "shift" nature of the LFSR is still readily apparent. The CASR has a different nature than the LFSR implementations and produces a noticeably different image. All three sequences are Maximal Length, which means that each cycles through all possible 13-bit numbers, except zero, before the sequence repeats.

Anchor Hill uses these techniques, and others, to assure the performance of generation of random sequences for channel modeling, noise modeling, data generation, encryption and other purposes. Complex systems are best verified in the lab with a combination of simulation and bench testing, and lab tests are far more effective when the channel environment is properly modelled. In our experience even the expensive, brand-name test equipment gets it very wrong sometimes, and verification of models and testing is critical. We have extensive experience with all phases of stochastic modeling and testing from field data collection for channel model generation to modeling to system simulation to bench testing and overall test strategy. Our test and verification methods have resulted in first-pass success in demodulator ASIC designs, successful demodulator FPGA cores for fixed and mobile communications, and board-level products with high reliability in field deployments. These skill-sets and techniques have also provided the basis for effective Built In System Test (BIST) features for factory and field test capability.

The images above were created during research for a noise generator with specific attributes that could be implemented efficiently in gates. The aesthetic qualities of the images are attractive to many and their true intent and usefulness subtle and esoteric. Anchor Hill often goes beyond the normal boundaries of practice to find unique solutions to unusual problems.

|

|

|

|